#### **Special Processes**

- wide variety of processes used in mems fabrication that are not "standard" IC fabrication

- anisotropic crystallographic etches

- KOH etch uses a mobile ionic contaminant!

- many processes used in other applications can be adapted

- laser drilling, laser sintering, injection molding, solid free-form fabrication, electric discharge machining (EDM), etc

- potential disadvantage for "volume" production: many of these are not "parallel" or "batch" processes

#### **Electrodeposition/electroplating**

- classical industrial process used to produce thin coatings

- almost always metal

- deposition is from the liquid phase, driven by an electrochemical reaction

- solution generally contains an ion of the metal (a "salt) that is easily reduced

- application of a negative bias to object to be plated (i.e., the object is the <u>cathode</u>) supplies the electrons necessary for reduction, resulting in deposition on the cathode

- local rate of deposition proportional to local current density

- J-V characteristic exhibits a saturation behavior

- above a certain applied voltage the current density saturates

- applied potential above this max tends to drive things like electrolysis of water, rather than reduction of the metal salt

- porous, poor quality deposition tends to result

- "black" metal at high current density

### **Electroplating examples**

- copper

- usually copper sulfate in sulfuric acid

- Cu<sup>2+</sup>(solution) + 2e<sup>-</sup> → Cu(solid)

- few mAmp / cm<sup>2</sup>

- gold

- usually gold cyanide solution

- $Au(CN)_2^- \Leftrightarrow AuCN + CN^-$

- AuCN +  $e^ \rightarrow$  Au(solid) + CN<sup>-</sup>

- few tens-hundred mA / cm<sup>2</sup>

- nickel

- nickel sulfate, boric acid

- masking

- photoresist or other non-conducting layer can be used

- for small, complex shapes must be careful about

- depletion of reactants

- non-uniformity in current density

- crystallographic orientation dependent growth rates

# Liga

- "Lithographie, Galvanoformung, Abformung"

- Ehrfeld et al, mid-80's; Guckel at Wisconsin

- "lithography, electroplating, and molding"

- really is just masked electroplating, but with high aspect ratio mask layers

- biggest challenge is the high aspect ratio lithography

- use X-ray proximity lithography

recall

$$l_{\min} \approx \frac{3}{2}\sqrt{gap\cdot\lambda}$$

- gap ~ thickness of resist ~ 100 $\mu$ m

- x-ray wavelength ~ 0.01 $\mu$ m

- $\Rightarrow$  *l*<sub>min</sub> ~ 1µm  $\Rightarrow$  100:1 aspect ratio feature

#### **Anodic oxidation**

- anodization

- sample connected to positive terminal of dc supply

- sample is the anode

- immersed in an electrolyte

- usually aqueous, but regardless oxidizing species is almost always (OH)<sup>-</sup>

- basic mechanism

- injection of holes into Si to form Si<sup>2+</sup> ("anodic" reaction)

- attachment of  $OH^{-}$  to the Si<sup>2+</sup> to form Si(OH)<sub>2</sub> (oxidation step)

- reaction of the "hydrated silica" to form oxide and hydrogen

- overall reaction for silicon oxidation

- Si + 2h<sup>+</sup> + 2H<sub>2</sub>O  $\rightarrow$  SiO<sub>2</sub> + 2H<sup>+</sup> + H<sub>2</sub>

- holes supplied by bias supply

- H<sup>+</sup> migrates to cathode, ultimately produces  $H_2$  at cathode

#### **Anodic oxidation kinetics**

- constant voltage bias

- thickness builds exponentially in time to a final asymptotic value

- $x = x_{\infty} (1 e^{-t/\tau})$

- for silicon  $x_{\infty} \sim 3\text{\AA}/\text{V}$

- i.e., for V =1000V the final thickness would be about 0.3  $\mu m$

- constant current bias

- thickness is linearly increasing in time

- voltage also increasing in time

- still have  $x_{\infty} \sim 3\text{\AA}/V$

### **Bonding processes**

- general requirements

- TCE match for dissimilar materials

- adhesives

- "bond line" thickness, long term hermeticity, out-gassing

- single component, multi-component, aerobic, anaerobic, UVcurable

- metal-glass seals

- with appropriate glass and metal choice extremely high quality bonds can be formed, but usually requires T ~ 1000°C

- silicon silicon fusion bonding

- usually fairly high temperature: ~1000C

- surfaces should be hydrophilic, interaction via "oxide" at interface

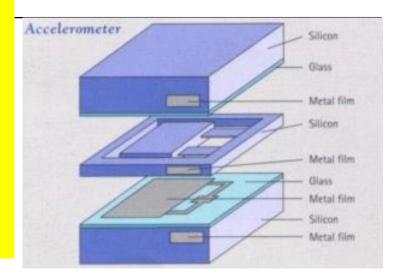

### **Anodic bonding**

- example: silicon to Pyrex 7740

- ~ 400°C, ~ 1kV applied voltage

- reasonable TCE match

- glass is ionic conductive at moderate temperatures

- current does flow, but electrode contacts are non-injecting

- at constant voltage, initial current is high (~mA/cm<sup>2</sup>), decays with time

- leads to depletion layer formation at silicon glass interface

- use electric field helps provide force to pull mating surfaces together

- actual bond via oxidation of silicon surface intermixing with glass surface

#### **Technical Data**

Wafer/Substrate Parameter:Up to 150mm Max. wafer stack thickness 4 mm Wafer/Substrate Configuration: Double stack: Silicon/Glass, Silicon/Silicon Triple stack: Any combination of Silicon and Glass Pressure Chamber: Over pressure: 2 bar (29 psi) Vacuum: 5 E-3 mbar – standard 1 E-5 mbar high vacuum optional Heater: 550 °C max. Voltage: 0 - 1200V / 50 mA optional up to 2000V / 50mA and 250V / 3A Contact Pressure: Up to 3.4 kN (765 lbf) optional up to 7 kN max (1570 lbf)

## wafer bonding

# Drying

- problem: for two closely spaced layers during rinsing and subsequent drying capillary forces may cause collapse and sticking (stiction)

- methods

- critical point drying

- at appropriate temperature, pressure liquid and gas are "same": supercritical region of phase diagram

- example: CO<sub>2</sub>: T > 31.1°C, P > 72.8 atm

- phase change drying

- freeze, then sublime

- low surface tension rinsing

- alcohol

- surface treatments